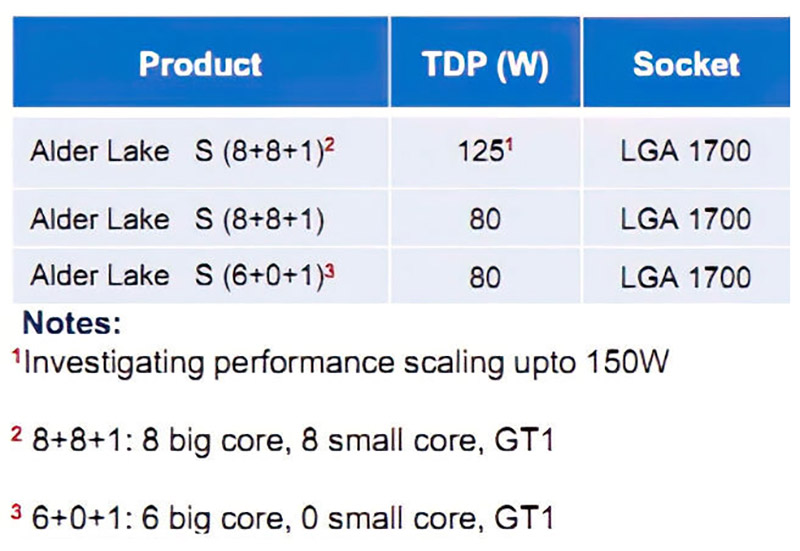

据海外网友爆料,英特尔在第十二代酷睿处理器,也就是代号Alder Lake-S的桌面处理器上,将会采用类似ARM模式的big.LITTLE大小核架构。爆料称,该处理器将会采用10nm制程工艺,拥有最多16颗核心,采用8+8的组合方式。同时,该处理器将会支持PCIe 4.0规范,采用LGA 1700接口,上市时间大概率会是2022年。

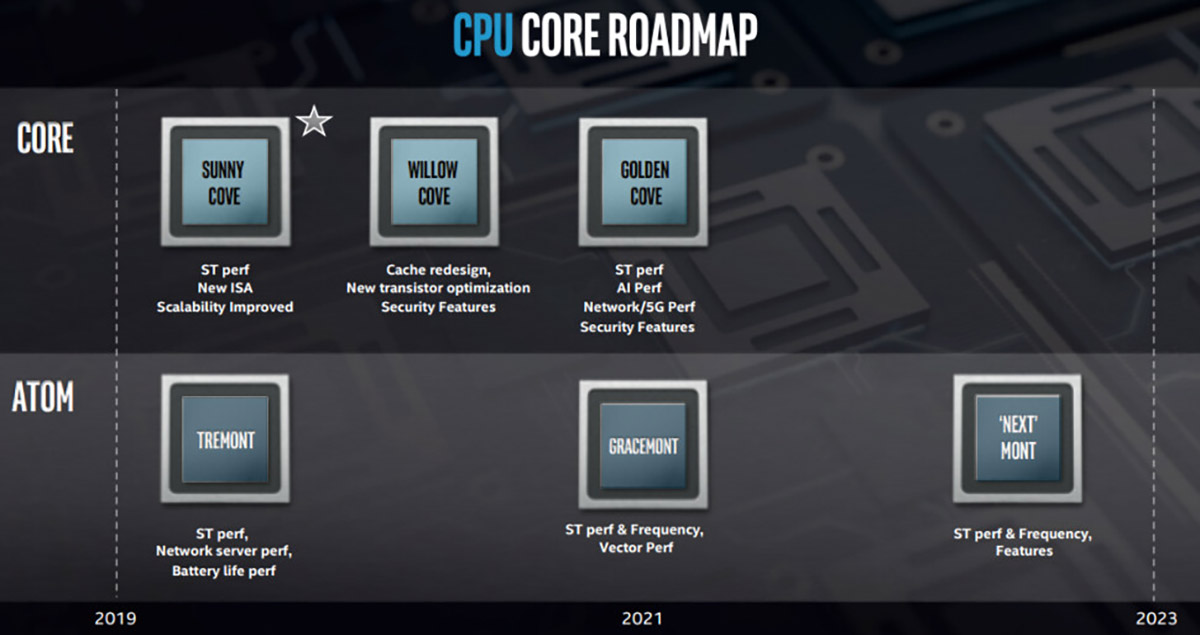

另外,网友猜测这16个核心不是一致的,而是包括8个大核心和8个小核心。大核心当然会采用目前英特尔酷睿处理器核心的升级版Golden Cove,而小核心不出意外的话将会是目前Atom低功耗处理器核心的升级Gracemont,英特尔在这两个产品线上都有深厚的积累。不过,这种选择其实会带来一定的调度性问题,需要操作系统和软件的优化,如果不解决好的话,会影响全核性能的发挥。

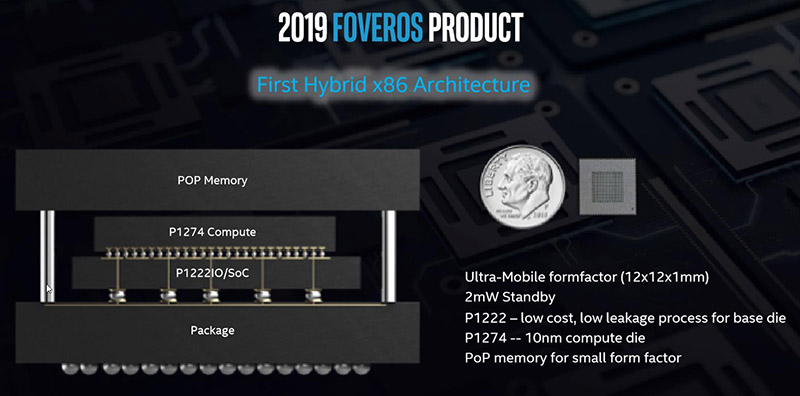

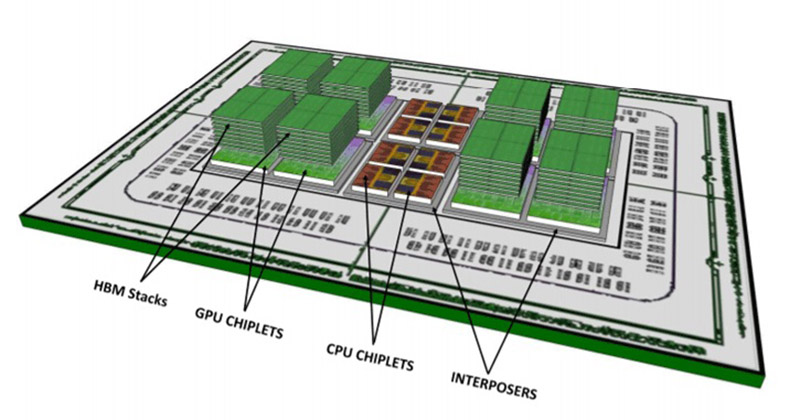

至于整合的方式也很成熟,应该就是英特尔已经推出了两年的Foveros 3D封装技术,目前已经被用于低功耗移动平台Lakefield上。该技术可以理解为晶圆级封装的进阶版,与台积电CoWoS封装技术类似,可以直接在晶圆上封装不同制程、不同功能的Die。

不过Foveros 3D封装技术其实更侧重于纵向堆叠,最大的优势在于缩小芯片面积,从而降低对空间的占用。这对于开发体型更小巧灵活的移动设备比较有价值,用于高性能台式机上似乎并不合适。反而是不同芯片组合封装的方式,在我看来更有价值一些。从某种意义上,这有点儿像是AMD的Chiplets的进阶版。如果发展到后期,英特尔将大核心、小核心、I/O和GPU分别独立成为小芯片封装在一个晶圆上,也是完全有可能的。毕竟,目前英特尔的封装技术已经比较成熟,同时也推出了自己独立的GPU芯片,在技术方面没有任何问题。

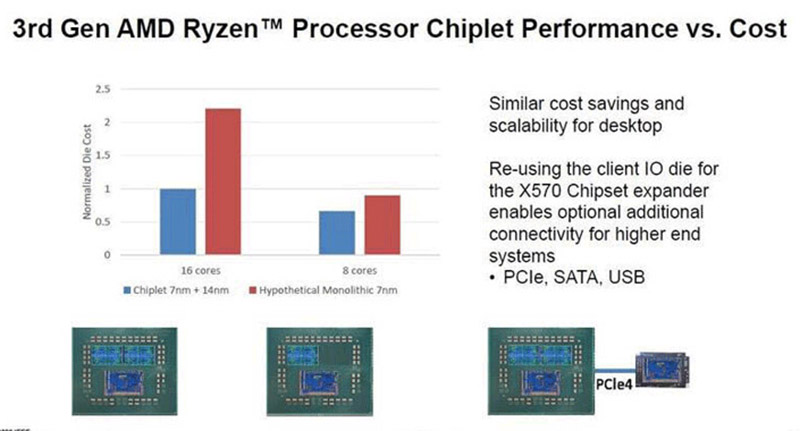

而从经济方面考虑,多个Die组合多芯片封装可以利用到相对落后的14nm、22nm产能,解决10nm工艺产能不足的问题。同时,每个Die的规模缩小,也有利于提高产品良率,降低多核心处理器的成本。之前AMD曾公开过相关数据,当芯片规模达到16核心时,小芯片封装将降低超过50%的成本,这意味着更便宜的处理器价格。

横排-无底-140x48mm-04-1.png)

竖排-无底白字-280x96mm-04.png)